# Comparação entre Tecnologias CMOS para implementação de portas lógicas

### Rafael Vieira Abrantes, Ernano Arrais Junior

Universidade Federal do Semi-Árido – Paus dos Feros – RN – Grupo de Desenvolvimento e Simulação - GDeS

rafael.abrantes.dm@hotmail.com, ernano.arrais@ufersa.edu.br

Abstract. The emergence of integrated circuits took place with the advancement of transistors, in particular field-effect transistors, especially MOSFETs (Metal Oxide Semiconductor Field Effect Transistor). Over the years, MOS transistors have been able to increase the density in a silicon wafer, so the miniaturization of the integrated circuits, however, is reaching the limit of the reduction of the size of the transistors. directed to more optimized topologies, presenting reduced number of transistors in a single application. The work uses the following standard and optimized logic ports, NOT, AND, OR, and XOR implemented in two ways, SPICE model and the layout of each logical port, comparing its response time.

Resumo. O surgimento dos circuitos integrados se realizou com o avanço dos transistores, em particular os transistores de efeito de campo, especialmente os MOSFET (Metal Oxide Semiconductor Field Effect Transistor). Com o passar dos anos, os transistores MOS possibilitaram o aumento da densidade em uma pastilha de silício, sendo assim, a miniaturização dos circuitos integrados, porém, se está chegando ao limite da redução do tamanho dos transistores, com isso, diversos trabalhos estão sendo direcionados a topologias mais otimizadas, apresentando quantidade reduzida de transistores em uma única aplicação. O trabalho utiliza as seguintes portas lógicas padrões e otimizadas, NOT, AND, OR e XOR implementado de duas formas, modelo SPICE e o layout de cada porta lógica, comparando o seu tempo de resposta.

# 1. Introdução

Com o advento dos elétrons no final do século XIX, iniciou-se a era na eletrônica, logo após as válvulas, sendo dispositivos amplificadores operavam com movimentos dos elétrons entre as placas em uma câmara a vácuo [OKA, 2000]. As válvulas persistiu seu uso por décadas, porém possuíam limitações, tempo de vida e tamanho grande, com isso, foram realizadas pesquisa para se obter dispositivos com maior eficiência. Em 1947, por Bardeen, Brattain e Shockley, substituindo as válvulas foi criado o primeiro transistor com maior eficiência e menor tamanho [RAZAVI, 2010].

O Transistor Bipolar de Junção (TBJ), o substituto das válvulas persistiu por mais de 3 décadas, por ser menor, mais rápido e menor custo [VAHID, 2008]. O TBJ foi destaque em projetos de circuitos até a chegada dos MOSFET (*Metal Oxide Semiconductor Field Effect Transistor*) [RAZAVI, 2010].

Ao decorrer do tempo, mesmo o TBJ com menor tamanho em relação com as válvulas, houve a necessidade de transistores menores, com isso, se obteve o agrupamento de vários de transistores em pastilha de silício, chamado de Circuito Integrado (CI), por volta da década de 60 [VAHID, 2006].

Nos Circuitos Integrados (CIs), um dos componentes utilizados é o MOSFET, com a capacidade de construir um CI com mais de 200 milhões de transistores, possuindo um vantagem em relação a transistores antigos, conseguem funcionar com baixa potência e serem miniaturizados com o passar dos anos [SEDRA, 2007]. O principal elemento para a criação do MOSFET é o silício, que na 28% da crosta terrestre contem este elemento semicondutor [VAHID, 2006].

Os CIs podem ser aplicados em elementos de lógica digital, até memória RAM e utiliza-los para construção de circuitos analógicos em comunicações. Em 1963, Frank Wanlass patenteou o *Complementary Metal Oxide Semiconductor (CMOS)* [PIMENTA, 2017]. O CMOS obteve avanço no mercado, com aproximadamente 75% dos componentes semicondutores são implementados utilizando a tecnologia [KOFUJI, 2017].

Este trabalho consiste na implementação das portas lógicas padrões e otimizadas, NOR, AND, OR e XOR, utilizando SPICE e posteriormente o *layout* de cada circuito, comparando o tempo de resposta entre as duas implementações com as seguintes litografías: 0,25 μm, 0,35 μm e 0,60 μm.

#### 2. MOSFET

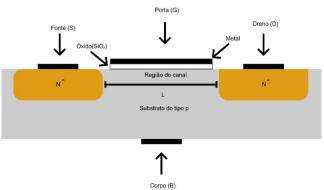

O Transistor de Efeito de Campo Metal-Óxido-Semicondutor (MOSFET) são fabricados com o elemento semicondutor, o silício dopado, possuindo mais elétrons ou mais lacunas (ausência de elétrons). O MOSFET possui 4 terminais, sendo eles, porta (*gate*), fonte (*source*), dreno (*drain*) e corpo (*body*), conforme mostra a Figura 1. Ao ser aplicado um tensão, se cria um fluxo de corrente entre o dreno e a fonte. [SEDRA, 2007].

Figura 1. Estrutura física do MOSFET. Fonte. Modificado de: Sedra (2007).

Com tensão aplicada, o MOSFET funciona em três regiões, de corte, tríodo e saturação. Quando o MOSFET se encontra em modo de corte ou tríodo, o transistor funciona como chave (transistor desligado ou ligado) e quando o transistor se encontra

no modo de saturação atua como fonte de corrente controlado por tensão. A tecnologia do transistor, ou seja, o tamanho do transistor se encontra pela relação entre W e L [SEDRA, 2007].

Para se projetar o MOS, consiste em definir as entradas e saídas do circuito, cálculos do projeto proposto, simulações, *layout* do circuito, reavaliação das entradas do circuito, testes e a fabricação [BAKER, 2004].

# 3. Tecnologia CMOS

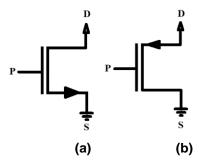

O CMOS possui inúmeras aplicações, por exemplo: a construção de portas lógicas digitais. O transistor CMOS possuem dois tipos: tipo p e tipo n, fisicamente, a diferença se encontra no corpo e na depleção do dreno e da fonte, sendo, do tipo p possuidores de mais lacunas e do tipo n possuidores de mais elétrons. O fluxo de corrente no canal são distintos, sendo que, no tipo p, a corrente percorre da fonte para o dreno e do tipo n do dreno para a fonte, conforme mostra a Figura 2.

Figura 2. (a) símbolo do NMOS e (b) símbolo do PMOS Fonte. SEDRA (2007).

Definir as áreas ativas, implementação da região dos poços, depositar e modelar as camadas de polisilício, realizar a implementação das regiões de dreno e fontes e a modelagem das camadas de metal, este processo é um resumo para a fabricação do CMOS [RASBAEY,2003].

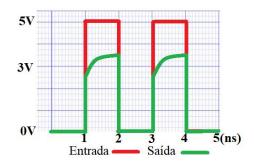

### 3.1. Transistor de Passagem

Os transistores de passagem de diferem dos convencionais, pois, o dreno e a fonte são polarizadas com valores lógicos, no caso do NMOS ao polarizar a fonte com o '0' lógico e o dreno com o '1' lógico se observa que o NMOS tem a facilidade de o '0' lógico, então, o NMOS passa o '0' bem. Os PMOS tem a facilidade de passar o '1' lógico [BAKER, 2007].

Figura 3: Gráfico tensão x tempo utilizando transistor de passagem NMOS.

Fonte: O autor.

# 3.2. Portas lógicas

Uma das aplicações de CMOS é implementando portas lógicas, NOT, AND, NAND, OR, NOR, XOR e XOR, com os transistores trabalhando como chave. Os resultados lógicos de cada porta se apresenta na Tabela 1.

Tabela 1. Tabela verdade das portas lógicas AND, NAND, OR, NOR, XOR e XNOR.

| A | В | AND | NAND | OR | NOR | XOR | XNOR |

|---|---|-----|------|----|-----|-----|------|

| 0 | 0 | 0   | 1    | 0  | 1   | 0   | 1    |

| 0 | 1 | 0   | 1    | 1  | 0   | 1   | 0    |

| 1 | 0 | 0   | 1    | 1  | 0   | 1   | 0    |

| 1 | 1 | 1   | 0    | 1  | 0   | 0   | 1    |

Fonte. Modificado de: Vahid (2008).

A porta lógica NOT é um inversor, quando a entrada for '1' (entrada alta) a saída será '0', a Tabela 1 apresenta o restantes das portas lógicas, a porta AND será '1' quando somente as duas entradas se encontram em '1', a NAND será o inverso da AND.

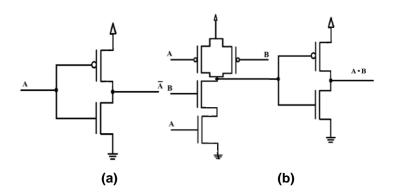

Neste trabalho apenas será trabalhado com as porta lógicas NOT, AND, OR e XOR, utilizando a tecnologia CMOS que o circuito padrão das seguintes porta são:

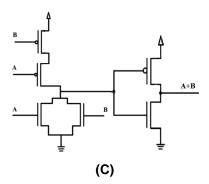

Figura 4. (a) Porta Lógica NOT, (b) Porta Lógica AND e (c) Porta Lógica OR. Fonte. Modificado de: VAHID (2008).

Na Figura 4 (a) à (c) encontra-se as portas lógicas padrões utilizando transistores, a Figura 4 (a) na porta lógica NOT ou inversor utiliza somente dois transistores, na porta lógica AND, Figura 4 (b), apresenta 6 transistores e dois deles trabalham como inversor e a porta lógica OR, Figura 4 (c), apresenta 6 transistores e dois deles trabalham como inversor, diferentemente da AND, as tensões nas portas são diferentes.

A porta lógica padrão XOR possui a seguinte equação:

$$X \oplus Y = \left(\overline{X} \bullet Y\right) + \left(\overline{Y} \bullet X\right) \tag{1}.$$

A equação 1 mostra que utiliza duas porta lógicas AND e uma OR para conseguir os resultados da XOR que sua saída será alta quando as duas entradas for distintas (RADHAKRISHANAN, 2001).

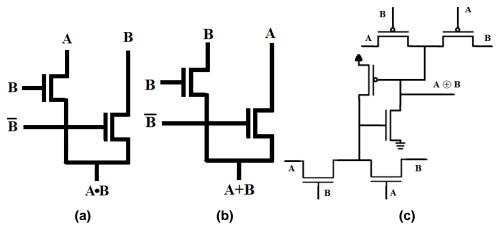

Para tentar minimizar a quantidades de transistores, alguns autores propuseram ou analisaram portas lógicas com menor quantidade de transistores conforme a Figura 5.

Figura 5. (a) Porta lógica AND otimizada, (b) Porta lógica OR otimizada e (c) Porta lógica XOR otimizada.

Fonte: (a), (b) MARKOVIC, NIKOLIC e OKLOBDZIJA (2000) e (c) RADHAKRISHANAN, 2001).

Na Figura 5 (a) à (c) apresenta as portas lógicas otimizadas com o máximo 6 transistores, sendo polarizado as partes dos componentes com as entradas A ou B.

#### 4. Resultados e Discussões

Foram analisados o tempo de resposta de cada porta lógica, NOT, AND, NOR e XOR padrão e otimizada, por método da implementação SPICE e o *layout* dos circuitos, todos em três tecnologias, 0,25 μm, 0,35 μm e 0,60 μm, e com comprimento (W) de 3 μm, 2 μm e 1,25 μm respectivamente, com as tensão de 2,5 V, 3,5 V e 5 V.

## 4.1. Implementação SPICE

A implementação SPICE é a descrição do circuito em linha de código, primeiro processo a ser realizado para a construção de um chip, sendo assim, pode-se obter os gráficos com os tempos de resposta das portas lógicas padrões e otimizadas, conforme mostra a Tabela 2 (ARRAIS, 2017).

Tabela 2. Atrasos das portas lógicas padrões e otimizadas com a implementação SPICE.

| Tecnologia/Porta lógica | NOT      | AND     | OR        | XOR       |                |  |

|-------------------------|----------|---------|-----------|-----------|----------------|--|

| 0,60 μm                 | 39 e 136 | 25 e 93 | 186 e 105 | 754 e 747 | Padrão (ps)    |  |

|                         |          | 28 e 40 | 52 e 38   | 117 e 100 | Otimizada (ps) |  |

| 0,35 μm                 | 17 e 82  | 71 e 35 | 89 e 70   | 473 e 549 | Padrão (ps)    |  |

|                         |          | 15 e 35 | 70 e 36   | 70 e 78   | Otimizada (ps) |  |

| 0,20 μm                 | 5 e 22   | 35 e 16 | 30 e 35   | 186 e 210 | Padrão (ps)    |  |

|                         |          | 3 e 27  | 41 e 22   | 76 e 36   | Otimizada (ps) |  |

Fonte. O autor.

Na Tabela 2, os dois tempos de cada comparação são, o primeiro tempo para a borda de subida e o segundo tempo para a borda de descida, com isso, analisa-se que o tempo de resposta diminuiu ao aumentar (diminuir o tamanho do transistor) a tecnologia e a porta lógica não foi obtido a parte otimizada.

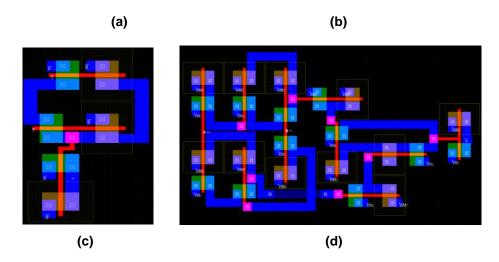

## 4.1. Layout

Outra etapa na fabricação de CI é a construção do *layout* do circuito, onde se utiliza um *software* que possui os componentes necessários. Se utiliza as cores para identificar os diversos componentes no CI. O *software* utilizado foi o MICROWIND e as cores para cada *layer* são, azul para o metal, vermelho para o polisilício, amarelo para região p+ e o preto que é a tela de fundo do *software* a região n+. O *layout* de cada circuito padrão se baseou-se na Figura 4 (a) à (c), conforme mostra a Figura 6 (a) a (d).

**ECOP 2018**, 19 a 21 de Março de 2018, Pau dos Ferros, RN – **ISSN 2526-7574** – v. 2, p. 153-161 https://periodicos.ufersa.edu.br/index.php/ecop

Figura 6. Layout da porta lógica (a) NOT, (b) OR, (c) AND e (d) XOR.

Com o *layout* padrão de cada circuito (Figura 6 (a) à (c)), observa-se que, cada circuito correspondeu a Tabela 1 e na Figura 6 (d) correspondeu o resultado esperado de acordo com a equação 2, porém, a quantidade de transistores é enorme com o total de 22 transistores.

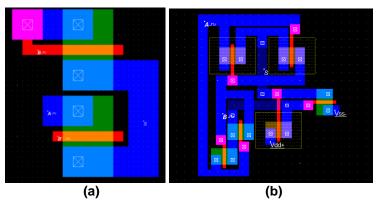

Logo após, foram obtidos o *layout* de cada circuito otimizado de acordo com a Figura 5 (a) à (c), conforme mostra a Figura 7 (a) e (b).

Figura 7. Portas lógicas otimizadas, (a) AND e OR e (b) XOR.

Na Figura 7 (a), o *layout* da porta lógica AND e OR são iguais, porém, as entradas são diferentes conforme são apresentas da Figura 5 (a) e (b). A porta lógica otimizada XOR da Figura 7 (b) possui somente os 6 transistores, 16 transistores a menos e apresentando o mesmo resultado na saída, porém, com tempo de resposta diferente, conforme a Tabela 3.

Tabela 3. Atrasos das portas lógicas padrões e otimizadas com a implementação SPICE.

| Tecnologia/Porta lógica | NOT      | AND     | OR        | XOR       |                |

|-------------------------|----------|---------|-----------|-----------|----------------|

| 0,60 μm                 | 39 e 136 | 25 e 93 | 186 e 105 | 754 e 747 | Padrão (ps)    |

|                         |          | 28 e 40 | 52 e 38   | 117 e 100 | Otimizada (ps) |

| 0,35 μm | 17 e 82 | 71 e 35 | 89 e 70 | 473 e 549 | Padrão (ps)    |  |

|---------|---------|---------|---------|-----------|----------------|--|

|         |         | 15 e 35 | 70 e 36 | 70 e 78   | Otimizada (ps) |  |

| 0,20 μm | 5 e 22  | 35 e 16 | 30 e 35 | 186 e 210 | Padrão (ps)    |  |

|         |         | 3 e 27  | 41 e 22 | 76 e 36   | Otimizada (ps) |  |

Fonte. O autor.

Ao comparar a Tabela 2 com a 3, observa-se que, o tempo de resposta do *layout* em relação SPICE foram próximos ou menores, e o mesmo aconteceu com o aumento da tecnologia o tempo de resposta foi diminuindo. Comparando os circuitos padrões e otimizados, o tempo foi reduzido em quase todos os casos, e quando não ocorreu na borda de subida o tempo foi menor na borda de descida ou vice-versa.

## 5. Conclusão

O tempo de resposta em cada circuito diminuiu em relação ao aumento da tecnologia e alguns *layouts* obtiveram mais eficiência em relação ao SPICE, sendo assim, pode-se avançar para o processo seguinte de fabricação. A utilização dos transistores de passagem resultou na deficiência na saída, mas mesmo assim o resultado digital foi correto. Com os resultados obtidos e os *layout*, posteriormente será utilizado para uma aplicação.

#### Referencias

- BAKER, Russel Jacob. **CMOS Circuit Design, Layout, And Simulation.** 2. ed. 2004. 1080 p.

- D. Radhakrishanan, Low-Voltage low-power CMOS full adder. In Proc. IEE Circuit Devices Syst., vol. 148, Feb. 2001.

- KOFUJI, Sérgio Takeo; ZUFFO, João Antonio; SOARES, João Navarro. Circuitos Integrados CMOS. 2015. Disponível em: <app.cear.ufpb.br/~asergio/Eletronica /Transistor/ Teoria-CMOS.pdf>. Acesso em: 03 mar. 2017.

- Markovic, D., Nikolic, B., and Oklobdzija, V.G., A general Method In Synthesis of Pass-Transistor Circuits. Microelectronics Journal, vol. 31, pp. 991-998, Nov. 2000.

- OKA, Mauricio Massazumi. **História do Transistor**. 2000. Disponível em: <a href="http://www.lsi.usp.br/~dmi/manuais/HistoriaDoTransistor.pdf">http://www.lsi.usp.br/~dmi/manuais/HistoriaDoTransistor.pdf</a>>. Acesso em: 10 out. 2017.

- PIMENTA, Tales Cleber. Circuitos Digitais: Análise e Síntese Lógica: Aplicações em FPGA. São Paulo: Elsevier Brasil, 2017. 592 p.

- RABAEY, Jan M.; CHANDRAKASAN, Anantha; NIKOLIC, Borivoje. **Digital Integrated Circuits: A design Perspective.** 2. Ed. [S.1]: Pearson, 2003. 761 p.

- RAZAVI,Behzad. **Design of analog CMOS integrated circuits.** Boston: McGraw-Hill, c2001. xx, 684 p.

- **ECOP 2018**, 19 a 21 de Março de 2018, Pau dos Ferros, RN **ISSN 2526-7574** v. 2, p. 153-161 https://periodicos.ufersa.edu.br/index.php/ecop

SEDRA, Adel S. Microeletrônica. Ed. -São Paulo: Pearson Prentice Hall, 2007.

VAHID, Frank. **Sistemas Digitais: Projeto, otimização e HDLs**. – Porto Alegre:Artmed, 2008. 560p.